GPU Hardware

Nvidia GPU Model

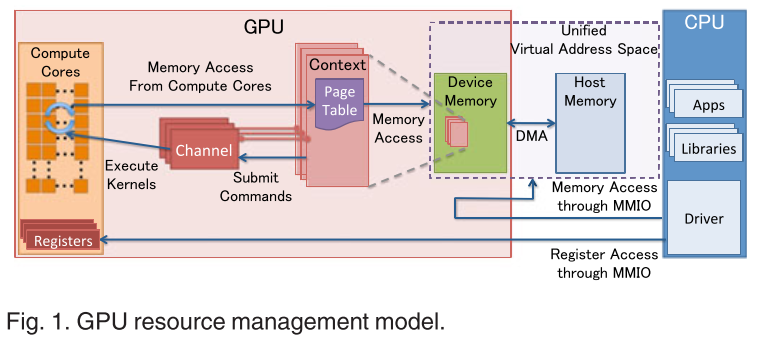

从上述图可以看出组成 GPU 的几个重要组成:

- MMIO:

- CPU 与 GPU 的交流就是通过 MMIO 进行的。

- DMA 传输大量的数据就是通过 MMIO 进行命令控制的

- I/O 端口可用于间接访问 MMIO 区域,像 Nouveau 等开源软件从来不访问它

- GPU context

- GPU context 代表了 GPU 计算的状态

- 在 GPU 上拥有自己的虚拟地址

- 在 GPU 上可以共存多种 context

- GPU channel

- 任何命令都是由 CPU 发出

- 命令流(command stream)被提交到硬件单元,也就是 GPU channel

- 每个 GPU channel 关联一个 context,而一个 GPU context 可以有多个 GPU channel。

- 每个 GPU context 包含相关 channel 的 GPU channel descriptors 。 每个 descriptor 都是 GPU 内存中的一个对象。

- 每个 GPU channel descriptor 存储了 channel 的设置,其中就包括 page table 。

- 在每个 GPU channel 中,在 GPU 内存中分配了唯一的命令缓存,这通过 MMIO 对 CPU 可见。

- GPU context switching 和命令执行都在 GPU 硬件内部调度。

- GPU Page Table

- GPU context 在虚拟基地空间由页表隔离其他的 context 。

- GPU 的页表隔离 CPU 页表,位于 GPU 内存中。

- GPU 页表的物理地址位于 GPU

channel descriptor中。 - GPU 页表不仅仅将 GPU 虚拟地址转换成 GPU 内存的物理地址,也可以转换成 CPU 的物理地址。因此,GPU 页表可以将 GPU 虚拟地址和 CPU 内存地址统一到 GPU 统一虚拟地址空间来。

- PCIe BAR

- GPU 设备通过 PCIe 总线接入到主机上。 base address registers(BARs) 是 MMIO 的窗口,在 GPU 启动时候配置。

- GPU 的控制寄存器和内存都映射到了 BARs 中。

- GPU 设备内存通过映射的 MMIO 窗口去配置 GPU 和访问 GPU 内存。

- PFIFO Engine

- PFIFO 是 GPU 命令提交通过的一个特殊的部件

- PFIFO 维护了一些独立命令队列,也就是

channel - 此命令队列是

ring buffer,有PUT和GET的指针。 - 所有访问

channel控制区域的执行指令都被 PFIFO 拦截下来。 - GPU 驱动使用

channel descriptor来存储相关的channel设定。 - PFIFO 将读取的命令转交给 PGRAPH engine

- BO

- Buffer Object (bo),内存的一块(block),能够用于存储 texture, a render target, shader code 等等。

- nouveau 和 gdev 经常使用 BO

Linked Mentions

-

No backlinks found.